使用 NativeLink 对英特尔 FPGA 进行功能仿真

如果要对英特尔 FPGA 的设计进行功能仿真,可能会使用 EDA 仿真器。本文我们将使用 Questa* - 英特尔 FPGA Edition (以下简称 Questa-IFE,包括 Starter Edition) 作为仿真工具的示例,在该工作流程中为大家进一步介绍 NativeLink 仿真。

什么是 NativeLink?

从 Quartus® Prime 运行 EDA 工具称为 NativeLink。例如,单击 Quartus Prime 菜单将自动出现 <Questa - IFE 启动、执行仿真所需的编译和加载、在波形窗口中显示仿真结果>,等等。不了解 IFE GUI 操作的人也可以很方便地进行模拟,对于想要提高操作效率的人来说也是非常推荐的使用流程。NativeLink 仿真还可以帮助用户自动加载 IP 模块功能仿真所需的所有仿真库。

NativeLink 支持环境和设置环境

可使用 NativeLink 的环境如下表 (表1) 所示:

| NativeLink 支持环境 (注1) | |

| 兼容的 Quartus Prime | Quartus Prime Standard Edition Quartus Prime Lite Edition *不支持专业版 |

| 支持的仿真工具 (注2) | ldec Active-HDL / Riviera-PRO Cadence Xcelium* 并行逻辑仿真 西门子 EDA ModelSim SE / Questa 高级模拟器 西门子 EDA Questa - 英特尔 FPGA 版 Synopsys VCS / VCS MX |

表1 NativeLink 支持环境

注1:所有原理图设计 (.bdf) 必须转换为 HDL。

注2:有关每个 EDA 工具支持的版本,需要查看正在使用的每个 Quartus Prime 版本的发行说明。

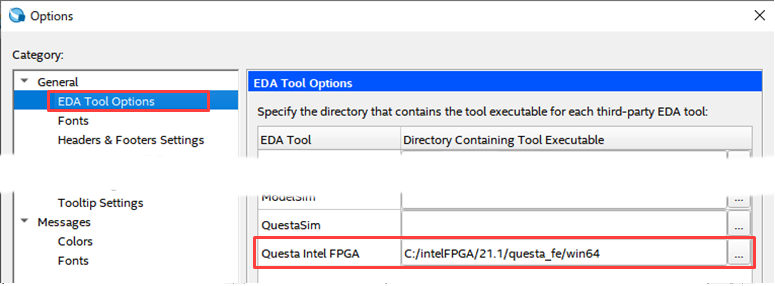

接下来开始设置运行 NativeLink 的环境。单击 Quartus Prime Tools 菜单 ,选择 Options 后点击 General 下的 EDA Tool Options,随后在如下图 (图1) 所示右边红框 Questa Intel FPGA 行单击最右侧的 [...] 按钮,指定保存可执行程序的文件夹的绝对路径。对于 Windows 操作系统,一般指定保存在 questasim.exe 的 win64 文件夹。

NativeLink 功能仿真工作流程

一、在 Quartus Prime 工程中编译 Quartus Prime 所需的所有设计

点击 Project 菜单,选择 Add/Remove Files in Project。如果这是对于不包含 IP 的设计,请继续步骤二。对于包含 IP 的设计,需要分为以下两种情况进行操作:

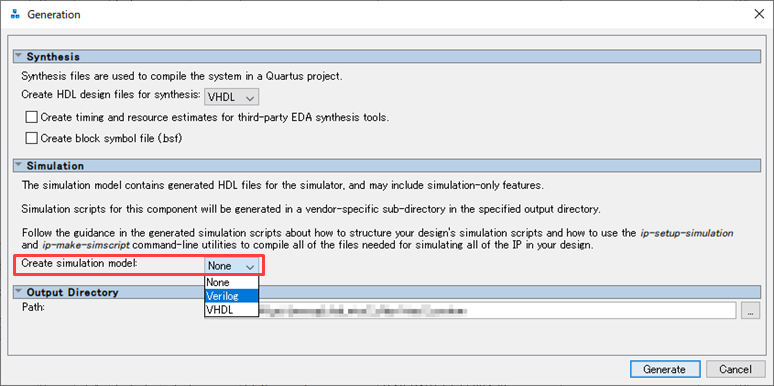

(1) 如果它包括使用 Platform Designer 创建的 IP,请在运行 Generate HDL 时弹出的 Generation 对话框中启用“Create simulation model”。选择要生成的语言后,单击“Generate” (或“Generate HDL”) 按钮还将生成仿真工具的功能模型,如下图 (图2) 所示:

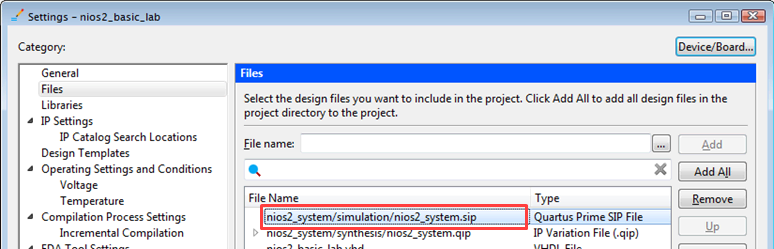

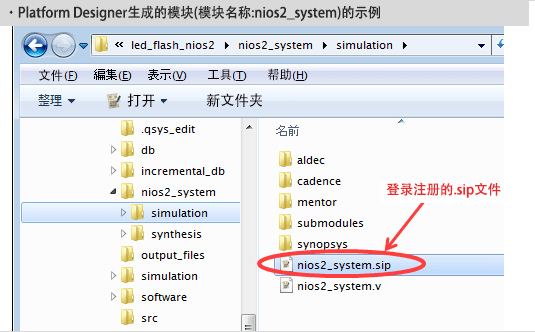

(2) 如果它包含在设计中,请确保使用下面的 Quartus Prime 菜单以与 <ip_name>.qip 相同的方式注册 <ip_name> .sip。点击 Project 菜单,选择 Add/Remove Files in Project。这里需要注意,通过从 IP Catalog 中选择 IP 并使用基于 MegaWizard Plug-In Manager 的 GUI 创建的 IP 模块不会生成 *.sip 文件,仅将 *.qip 文件注册到项目中即可,如下图 (图3) 所示。生成 .sip 文件的位置取决于使用 IP Catalog 还是 Platform Designer 创建 IP 模块。

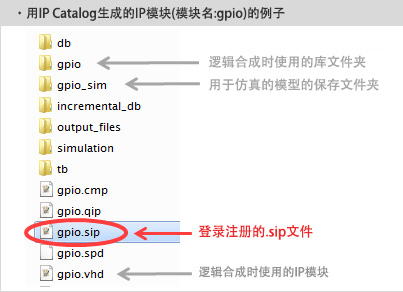

假如使用的是 IP Catalog 创建的 IP 模块,则是在生成 <ip_name>.v (或 .vhd) 的文件夹中生成 .sip 文件,其位置在与 <ip_name>_sim 文件夹相同的文件夹中,下图 (图4) 为它的文件夹结构:

假如使用的是 Platform Designer 创建的 IP 模块,那么其文件夹结构如下图 (图5) 所示,它是在 <ip_name>. 文件夹中的 simulation 文件夹中生成 .sip 文件。

二、EDA 编写设置

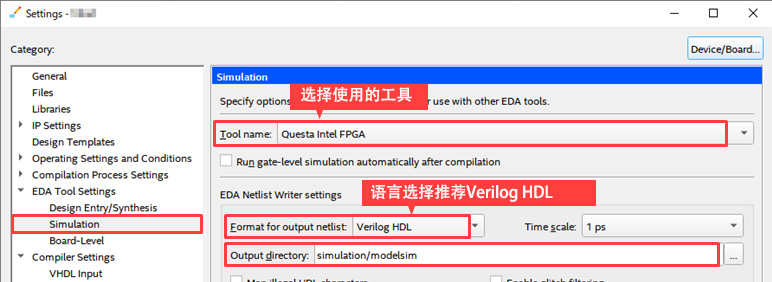

选择 Assignments➤Settings➤EDA Tool Settings➤Simulation,并在 EDA Netlist Writer 设置中设置以下项目。下图 (图6) 显示了 EDA 编写设置:

- Tool name:Questa Intel FPGA (*入门版也选择这个)

- Format for output netlist:Verilog HDL

- Output directory:simulation/modelsim (建议保留默认)

在 Format for output netlist 中,即使创建 IP 时使用的仿真模型或测试平台是 VHDL,建议在这里也选择 Verilog HDL 作为选项,此语言选择会影响 NativeLink 执行脚本中的 vsim-L 命令。有时会遇到即使最新 IP 的仿真模型的语言选择指定为 VHDL,但下层模型往往是在 SystemVeriog 中配置的,不可避免地需要 Verilog HDL 的仿真库。在这种情况下,需要使用 vsim-L 命令指定 Verilog HDL 的所有库,因此即使在 VHDL 中生成模型,也请使用 Verilog HDL 作为 Format for output netlist 的格式。

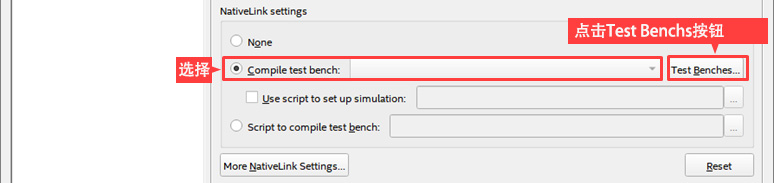

三、在 NativeLink settings 中注册测试台

根据下图 (图7) 所示,设置 NativeLink settings,选择 Compile test bench 并单击 Test Benches 按钮。

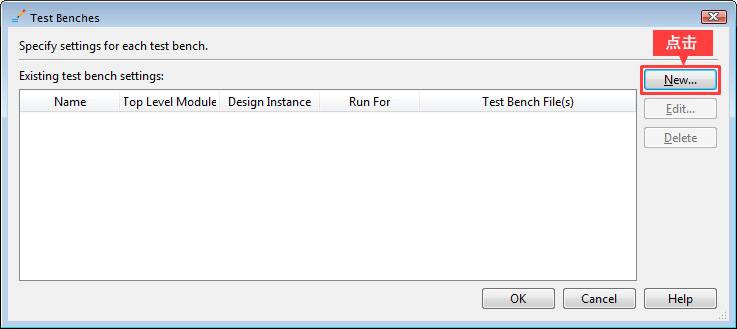

随后单击 Test Benches 窗口中的 New 按钮,如下图 (图8) 所示:

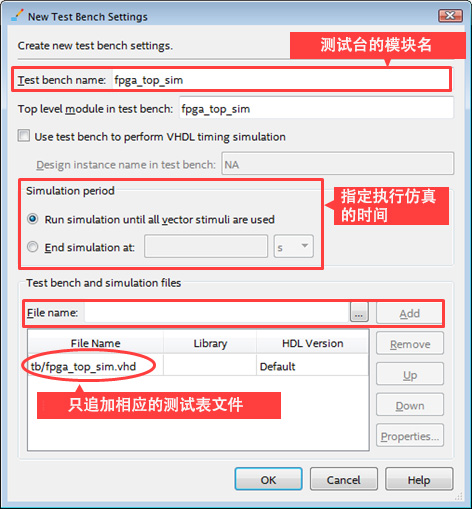

接下来在 New Test Benches Settings 对话框中设置如下图 (图9) 所示项目后单击确定关闭每个窗口以返回 Settings 窗口。

- Test bench name:输入测试台的模块名称 (也可输入底部 Top Level module in test bench)

- Simulation period:设定仿真执行的结束时间

- File name:点击最右侧的 [...] 按钮,选择测试台文件,使用 Add 按钮注册

四、使用 NativeLink 运行功能仿真

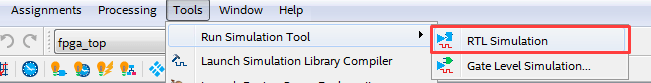

如下图 (图10) 所示,单击 Tools 菜单➤Run Simulation Tool➤RTL Simulation。在这个过程中,请注意:要运行 RTL Simulation,必须提前运行 Analysis & Elaboration、Analysis & Synthesis 或 Fitter 流程,但不要运行 Start Compilation (Processing 菜单),EDA Netlist Writer 自动运行不会生成成功的 RTL Simulation 脚本。如果已执行完整编译,请再次运行 Analysis & Elaboration、Analysis & Synthesis 或 Fitter 后运行 RTL Simulation。

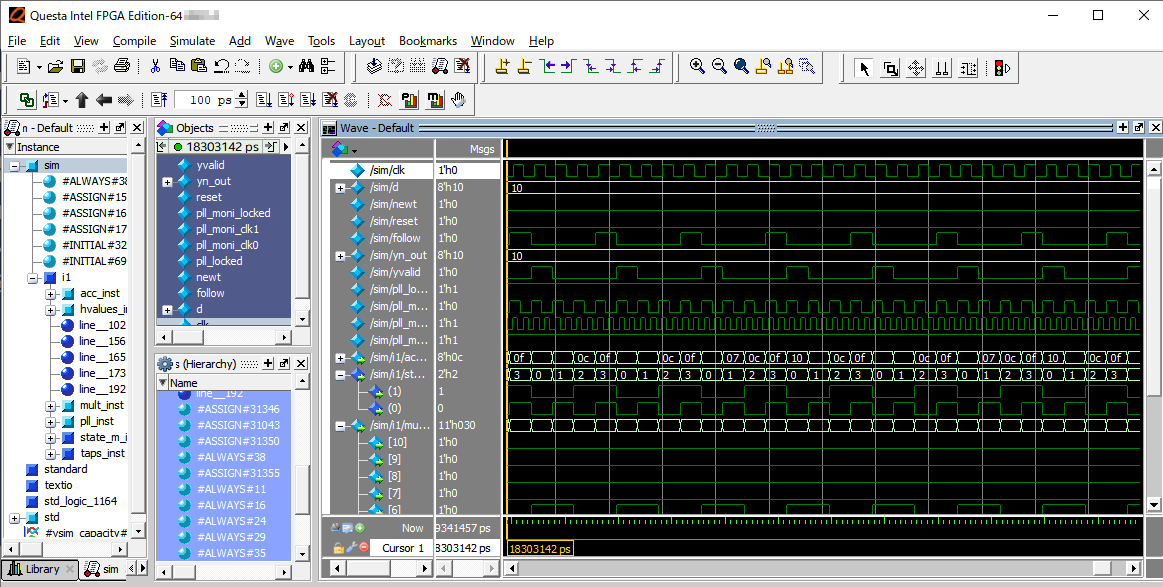

Questa - 在 IFE 中编译、应用和加载程序库,在 Wave 窗口中添加信号并运行仿真,所有这些操作都是自动进行的,波形最终会显示在 Wave 窗口中,如下图 (图11) 所示。使用 NativeLink 进行功能仿真,用户只需检查 Wave 窗口即可,实现了效率的提升。

总结

本文以使用英特尔 Questa-IFE 为仿真示例,介绍了 NativeLink 的功能特点、支持环境、设置环境和运行功能仿真的流程。欲了解更多英特尔相关方案或技术信息,可点击下方「联系我们」,提交您的需求,骏龙科技公司愿意为您提供更详细的技术解答。

更多信息: