如何使用 Intel FPGA 系统调试工具 System Console

英特尔 System Console 是 Quartus® Prime 附带的调试工具,在进行 FPGA 设计时,它可以帮助用户快速、高效地调试设计,例如:通过 JTAG 调试设计,JTAG 访问连接到 System Console 的外设的寄存器,检查 JTAG 主机的时钟等。此外,即使用户未安装 Nios® II 处理器,也可使用 System Console 调试简单的寄存器访问,本文将通过一个简单的示例为大家介绍 System Console。

System Console 目标环境和使用要求

下表 (表1) 为 System Console 的目标环境:

| Quartus Prime | 专业版 (Pro Edition) / 标准版 (Standard Edition) / 精简版 (Lite Edition) |

| 目标设备 | Quartus Prime 版本支持的所有器件 |

| 通信电缆 | USB-Blaster II USB-Blaster |

表1 System Console 目标环境

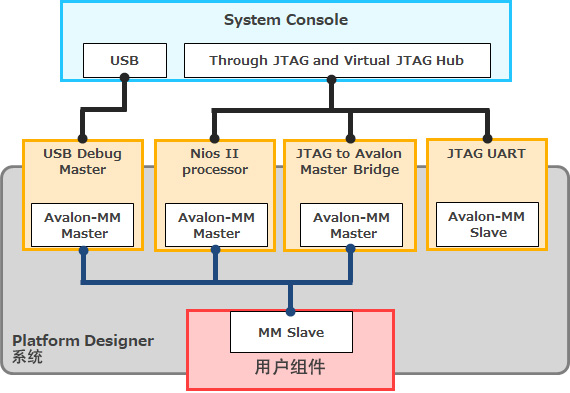

下图 (图1) 为 System Console 的设备组成示意图,如果要在项目设计中使用 System Console,那么项目设计中需要包含以下外围设备之一:

- Avalon-ST (Streaming) JTAG Interface

- Nios ® II 处理器 (带 JTAG 调试模块)

- JTAG to Avalon® Master Bridge

- USB Debug Master

- JTAG UART

- 以太网组件

示例设计

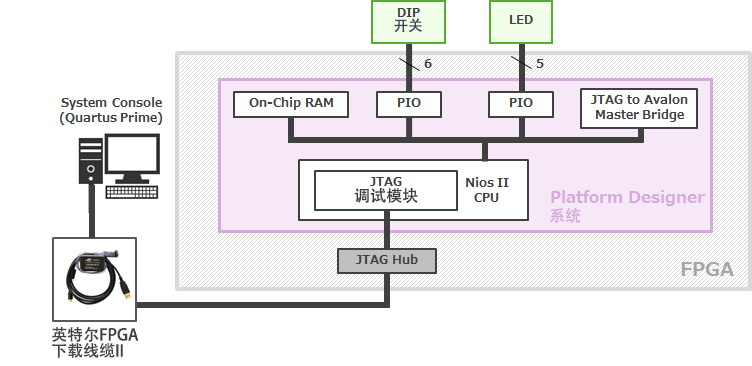

接下来将使用 System Console 来检查时钟信号和复位信号的状态,并访问 DIP 开关 PIO、LED PIO 和片内 RAM。这次将使用 Quartus Prime Standard Edition GUI 进行操作,下图 (图2) 为示例设计配置图:

System Console 调试流程

完成配置后即可使用 System Console 进行调试,其工作流程如下:

一、在 Platform Designer 系统中添加并生成 IP 核

将使用 System Console 所需的 IP 合并到 Platform Designer 系统中,本次示例设计中使用到的组件如下:

- Nios II Processor (带 JTAG Debug 模块)

- JTAG to Avalon Master Bridge

- On-Chip Memory Intel FPGA IP

- PIO Intel FPGA IP (2 个)

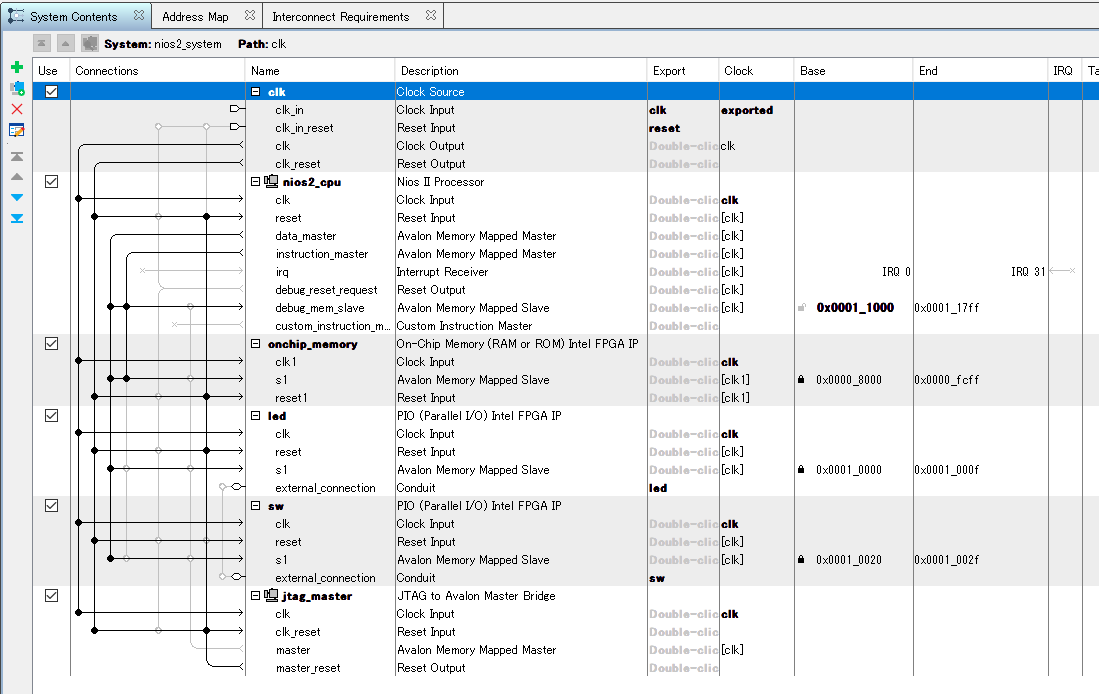

需要注意的是,如果只有简单的寄存器访问,可以单独使用 Nios II 进行调试,在这种情况下还需要连接 JTAG to Avalon Master Bridge,以便使用 JTAG Debug 服务 (命令)。在 Platform Designer 中注册每个组件后,在 “System Contents” 选项卡中将其连接。将 Avalon Memory Mapped Master (以下简称 Avalon MM Master) 连接到要操作组件的 Avalon Memory Mapped Slave (以下简称 Avalon MM Slave)。但此示例设计指定在 Nios II 的 Avalon MM Master 上执行 Master 服务。JTAG 调试服务由 JTAG to Avalon Master Bridge 的 Avalon MM Master 执行,下图 (图3) 显示了此示例设计中的连接。完成后,保存 Platform Designer 系统并运行生成 HDL。

二、编译设计

将创建的 Platform Designer 系统合并到设计中,并将其注册到项目中,然后运行编译。

三、连接电路板并配置 FPGA

(1) 将开发板连接到下载线,然后打开开发板的电源;

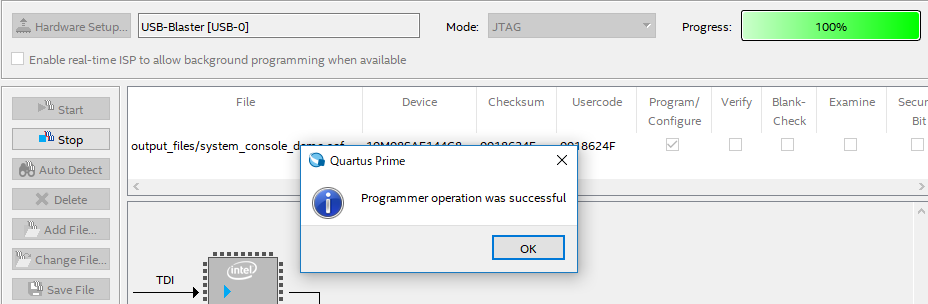

(2) 启动 Quartus Prime Programmer,选择要下载的 Hardware Setup 和 sof 文件,配置各种设置;

(3) 点击 Start 按钮完成配置后出现如下图 (图4) 页面;

(4) 关闭编程器。请注意在此处不执行 FPGA 配置 (下载 .sof),可以使用 System Console 中的设备命令 device_download_sof 完成 FPGA 配置。

四、启动 System Console

下面提供了三种可启动 System Console 的方法,工程师可根据系统的开发状况选择适合的启动方式:

- Quartus Prime Tools 菜单 > System Debugging Tools > System Console

- 启动 Nios II Command Shell 并输入 system-console.exe 命令

- Platform Designer Tools 菜单 > System Console

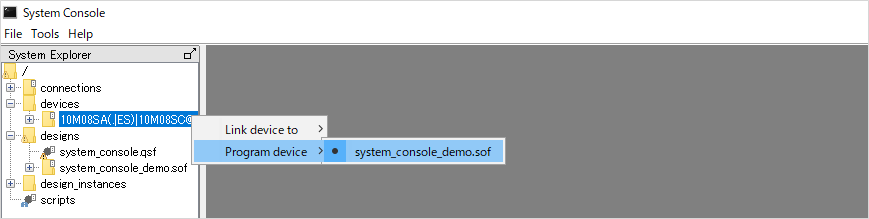

接下来单击 System Console 的 File 菜单 > Load Design 后选择要下载的 .sof。如果已经下载了 .sof,请右键单击 > Program device > “sof 文件”,可在 System Explorer 窗格中 devices 文件夹下查看与之连接的 FPGA,如下图 (图5) 所示:

或者也可以通过在 Tcl Console 窗格中输入以下命令来配置 FPGA:

% get_service_paths device

% set dpath [lindex [get_service_paths device] 0]

% device_download_sof $dpath "sof fifile path"

五、指定服务路径并标识服务

在 Tcl Console 窗格中,使用 get_service_paths 命令指定路径以标识服务,并可以使用 get_service_types 命令检查服务类型列表。例如在此示例设计中,如果要访问 DIP 开关的 PIO、LED 的 PIO 和片上 RAM,请使用主服务,通过输入以下命令以获取主服务的路径:

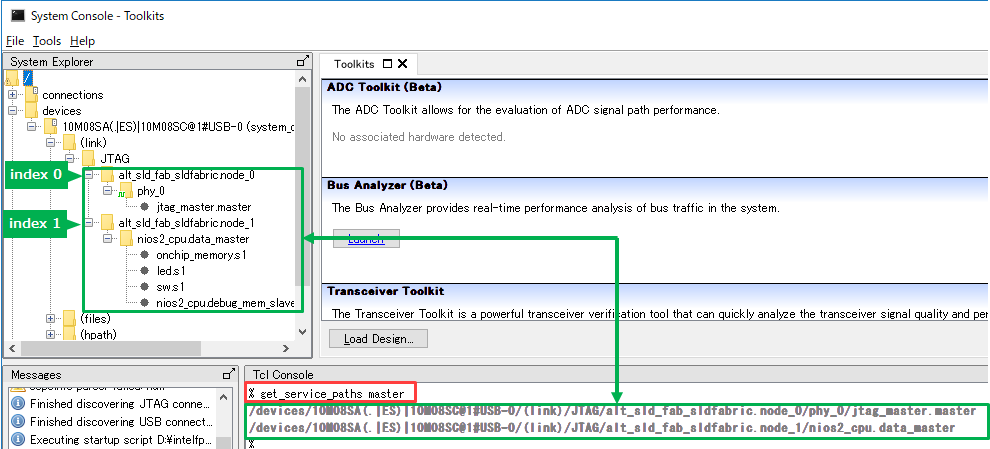

% get_service_paths master

如下图 (图6) 所示,在示例设计中,显示了两个 Avalon MM Master。除了上述命令的日志外,还可以在 System Explorer 窗格中 devices 文件夹 > 在 FPGA 型号 > (link) 文件夹下以及 JTAG 文件夹下检查它。

在示例设计中,每个内存映射的从站都通过 Nios II 的 Avalon MM Master 进行读写,所以可以通过输入以下命令创建指向 Nios II (Avalon MM Master) 组件的变量。在这里 mpath 是一个变量,lindex 为 1。

% set mpath [lindex [get_service_paths master] 1]

六、启动服务

claim_service 命令将启动与指定服务的连接:

% claim_service master $mpath ""

为了方便后续调试,请在使用以下命令启动的服务中创建变量:

% set master_path [claim_service master $mpath ""]

注意:如果使用上述命令,则无需同时使用 claim_service master $mpath“”。

七、执行调试操作

以下通过展示本次示例中的一些示例说明使用该命令验证连接的设备:

● 检查时钟和复位信号/发出复位信号

可以使用 jtag_debug 服务检查时钟和复位信号/发出复位信号。在示例设计中,是通过 JTAG 的 Avalon MM Master 访问 Avalon Master Bridge。在此命令中,jdpath 是一个变量,Lindex 为 0。

% set jdpath [lindex [get_service_paths jtag_debug] 0]

% jtag_debug_sample_clock $jdpath

% jtag_debug_sample_reset $jdpath

% jtag_debug_reset_system $jdpath

其中,jtag_debug_sample_clock 为:返回时钟信号的值 (切换确认需要多次采样);jtag_debug_sample_reset 为:返回复位信号的值;jtag_debug_reset_system 为:向连接到 Avalon to JTAG Master 的所有组件发出复位信号。

● 检查拨码开关的 ON/OFF 状态

% master_read_8 $master_path 0x10020 1

其中,master_read_8 为:读取指定地址的值;0x10020 为:DIP 开关的 PIO 地址;1 为:读数尺寸。

● 控制 LED 开关

% master_write_8 $master_path 0x10000 0x1F

% master_write_8 $master_path 0x10000 0x0

其中,master_write_8 为:写入指定地址;0x10000 为:LED 用 PIO 地址;0x1F、0X0 为:要写入的值。

● 读写片上 RAM

% master_read_32 $master_path 0x8000 32

其中,master_read_32 为:读取指定地址的值;0x80000 为:片上 RAM 的地址;32 为:读出尺寸。

% master_write_32 $master_path 0x8000 {0 1 2 3 4 5 6 7 8 9 10}

其中,master_wrote_32 为:写入指定地址的值;0x80000 为:片上 RAM 的地址;{0 1 2 3 4 5 6 7 8 9 10} 为:要写入的值。有关更多命令和服务,请参阅以下表 (表2) 文档:

| Quartus Prime版本 | 参考文档 |

Standard Edition Lite Edition |

摘自《Intel Quartus Prime 标准版用户指南:调试工具》 |

| Pro Edition |

摘自《Intel Quartus Prime Pro Edition 用户指南:调试工具》 |

表2 参考文档

8、服务终止

使用 close_service 命令将关闭与步骤 6 中启动的服务的连接。

% close_service master $master_path

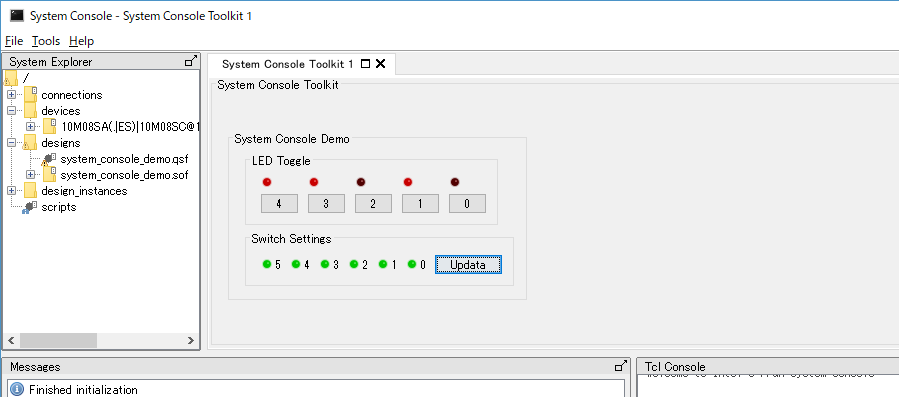

使用 Toolkit API 运行应用

下图 (图7) 为 System Console Toolkit 图,通过使用 Toolkit API 服务编写需要在 System Console 的 Tcl Console 窗格中键入的命令脚本,可以将调试数据可视化,并通过使用图形元素 (例如按钮、文本框、条形图和刻度盘) 把它们显示出来。

总结

英特尔 System Console 可允许将系统级读/写事务发送到 Platform Designer 系统,从而帮助工程师隔离和确定问题,它还提供一种简单快速的检查系统时钟和监控复位状态的方法,这在电路板初启阶段特别有用。欲了解更多英特尔相关方案或技术信息,可点击下方「联系我们」,提交您的需求,骏龙科技公司愿意为您提供更详细的技术解答。

更多信息: