深入探索 Altera FPGA AI Suite 範例設計:加速您的 AI 推論應用

前言

Altera FPGA AI Suite 提供了一套完整的解決方案,旨在加速在 Intel FPGA 上部署人工智慧 (AI) 推論。透過其強大的工具、IP 核心和豐富的範例設計,開發人員可以快速上手並充分利用 FPGA 的彈性和效能優勢。本文將深入探討 FPGA AI Suite 中幾個關鍵的範例設計,展示如何在不同應用場景下加速 AI 推論,並提供相關的圖表及其出處,以增強理解。

FPGA AI Suite 組成概覽

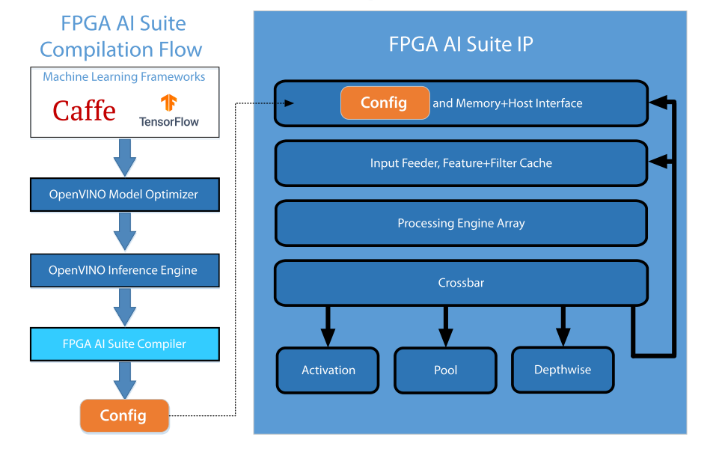

在介紹範例設計之前,我們先簡要回顧 FPGA AI Suite 的主要組成部分:

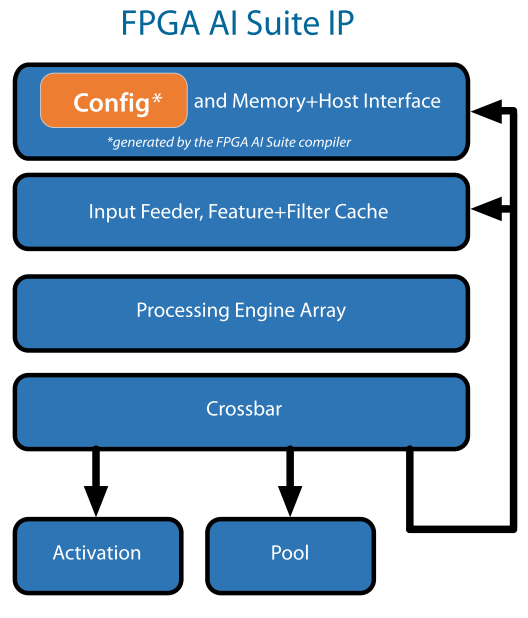

- FPGA AI Suite IP:一個可客製化的 RTL IP 核心,具有 AXI 介面,可整合到 FPGA 系統中,作為 AI 推論的硬體加速引擎。IP 的行為和效能由架構描述檔案 (.arch) 定義。

- 編譯器 (dla_compiler):一個多用途工具,用於將訓練好的 AI 模型(通常為 OpenVINO IR 格式,即 .xml 和 .bin 檔案)轉換為 FPGA AI Suite IP 可執行的配置,並進行效能和資源預估,以及 IP 架構的優化。

- IP 產生工具:根據架構描述檔案產生 FPGA AI Suite IP 的函式庫,方便在 FPGA 設計工具(如 Quartus Platform Designer)中導入和使用。

範例設計:展示如何使用 FPGA AI Suite IP 的完整設計專案,涵蓋不同的應用場景和硬體平台。

圖一 FPGA AI Suite 的主要組件及其流程

圖一 FPGA AI Suite 的主要組件及其流程

FPGA AI Suite 提供的範例設計是學習和掌握該工具套件的寶貴資源。它們不僅展示了 FPGA AI Suite IP 的實際應用方式,還提供了可直接建置、執行和修改的程式碼,幫助開發人員快速理解 AI 模型在 FPGA 上的部署流程和不同加速模型的實現。

主要範例設計介紹

FPGA AI Suite 包含了多個針對不同 Intel FPGA 系列和應用場景的範例設計。以下將介紹幾個主要的範例:

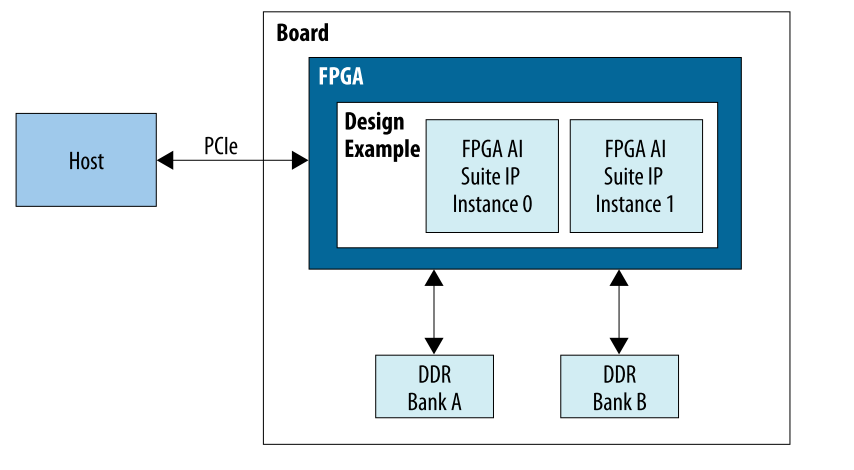

- 基於 PCIe 的 Agilex 7 範例設計:

- 目標平台:Terasic DE10-Agilex 開發板 (DE10-Agilex-B2E2)。

- 應用場景:展示 look-aside 深度學習加速模型,其中主機 (透過 PCIe 介面連接) 將 AI 推論任務卸載到 FPGA 上的 FPGA AI Suite IP。

- 關鍵組件:包含 FPGA AI Suite IP 和 Intel Distribution of OpenVINO toolkit。此範例使用了 FPGA AI Suite runtime plugin.

- 功能特色:此範例展示了如何在 FPGA 設計中實例化 FPGA AI Suite IP,並提供了一個範例 runtime,說明如何控制 IP、載入模型配置以及運行推論。開發人員可以使用 dla_benchmark 應用程式來評估加速效能。此範例也包含預建的 FPGA 位元流,並允許開發人員使用 dla_build_example_design.py 工具,根據不同的架構檔案 (.arch) 建立自己的位元流。

- 快速入門:使用者應首先參閱《FPGA AI Suite Getting Started Guide》以完成安裝和預備步驟。更詳細的建置和執行步驟可在《FPGA AI Suite PCIe-based Design Example User Guide》中找到。

圖二 基於 PCIe 的 Agilex 7 範例設計系統架構圖

圖二 基於 PCIe 的 Agilex 7 範例設計系統架構圖

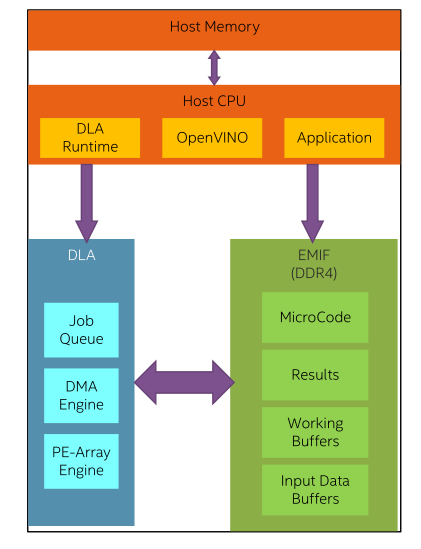

- 基於 SoC 的 Arria 10 和 Agilex 7 範例設計:

- 目標平台:Arria 10 SX SoC FPGA 開發套件 (DK-SOC-10AS066S) 和 Agilex 7 FPGA I-Series Transceiver-SoC 開發套件 (DK-SI-AGI027FC)。

- 應用場景:展示 CPU-offload 深度學習加速模型,在嵌入式系統中使用 SoC 中的 ARM 處理器作為主機,將 AI 推論任務卸載到 FPGA fabric 中的 FPGA AI Suite IP。

- 關鍵組件:包含 FPGA AI Suite IP、Intel Distribution of OpenVINO toolkit 和社群支援的 OpenVINO ARM 外掛程式。此範例使用了 Yocto frameworks 建立的 Arm*-Linux 系統.

- 功能特色:此範例展示了如何在 SoC 架構中使用 FPGA AI Suite IP,並提供記憶體到記憶體 (M2M) 和 串流到記憶體 (S2M) 兩種資料流模式。使用者可以運行 dla_benchmark 工具來評估效能。

- 快速入門:使用者可以參考《FPGA AI Suite SoC Design Example User Guide》中的快速入門教程。詳細的建置和執行步驟也在該指南中.

圖三 基於 SoC 的 Agilex 7 範例設計系統架構圖

圖三 基於 SoC 的 Agilex 7 範例設計系統架構圖

- Agilex 7-I 系列的 Hostless DDR-Free 範例設計:

- 目標平台:Agilex 7 FPGA I-Series Development Kit ES2 (DK-DEV-AGI027RBES)。

- 應用場景:展示無需外部 DDR 記憶體 的 AI 推論,適用於低成本和低功耗的邊緣運算應用。

- 功能特色:在此範例中,輸入和輸出資料直接串流進出 FPGA AI Suite IP。IP 的控制透過 Quartus Prime System Console 手動完成。這種類型被稱為 DDR-free 以取代先前的 "memoryless".

- 優勢:這種設計降低了對外部記憶體的需求,簡化了硬體設計,並可能降低功耗.

- Agilex 5 E-Series 的 JTAG 範例設計:

- 目標平台:Agilex 5 FPGA E-Series 065B Premium Development Kit (DK-A5E065BB32AES1)。

- 應用場景:展示如何在 Agilex 5 E-Series 裝置上實例化 FPGA AI Suite IP。

- 功能特色:此範例將配置和資料放置在外部 DDR 記憶體中,並允許外部主機透過 JTAG 介面與記憶體和 FPGA AI Suite IP 互動。

- Agilex 7-I 系列的 Hostless DDR-Free 範例設計:

圖四 FPGA AI Suite IP 的高階架構圖

圖四 FPGA AI Suite IP 的高階架構圖

範例設計所展示的共通概念

透過研究這些範例設計,開發人員可以學習到許多關鍵概念:

- FPGA AI Suite IP 的實例化和配置,包括如何使用架構描述檔案 (.arch).

- FPGA AI Suite runtime 環境的建置和使用.

- 主機軟體與 FPGA AI Suite IP 的互動方式 (例如透過 PCIe 或 AXI 介面).

- 不同加速模型的實現 (例如 look-aside 和 CPU-offload).

- 如何使用 FPGA AI Suite 工具進行效能評估 (例如 dla_benchmark).

- 針對特定硬體平台建立 FPGA 位元流的流程.

- DDR 記憶體和串流資料的處理方式.

OpenVINO 工具套件在 AI 模型轉換和部署中的作用.

開始使用範例設計

若要開始使用 FPGA AI Suite 的範例設計,建議遵循以下步驟:

- 查閱相關文件:《FPGA AI Suite Getting Started Guide》、《FPGA AI Suite PCIe-based Design Example User Guide》、《FPGA AI Suite SoC Design Example User Guide》 等文件包含了詳細的說明、先決條件和建置步驟。

- 確認硬體和軟體先決條件:確保您擁有對應的 FPGA 開發板,並安裝了所需的軟體工具,例如 Quartus Prime Pro Edition 和 Intel Distribution of OpenVINO toolkit。FPGA AI Suite 2024.3 版本需要 Intel Distribution of OpenVINO toolkit 2023.3 LTS.

- 按照使用者指南中的指示進行操作:每個範例設計都有其特定的建置和執行流程,請仔細閱讀相關的使用者指南.

嘗試修改和擴展範例:在理解範例設計的基礎上,嘗試修改程式碼、更換不同的 AI 模型 或調整 IP 配置 (.arch 檔案),以加深理解並應用於您的專案。可以參考《FPGA AI Suite Compiler Reference Manual》 和《FPGA AI Suite IP Reference Manual》 了解更多關於編譯器和 IP 的細節。

結論

FPGA AI Suite 提供的範例設計是學習和應用這項強大技術的絕佳起點。透過研究和實作這些範例,開發人員可以快速掌握在 Intel FPGA 上加速 AI 推論的關鍵技術,並為各種應用開發高效能、低功耗的客製化 AI 解決方案。無論您的目標是邊緣運算、嵌入式系統 還是資料中心應用,FPGA AI Suite 的範例設計都能為您提供寶貴的參考和實作基礎。