Mpression - Industrial Machine Vision - FPGA IP Products

- SLVS-EC

- CoaxPress

SLVS-EC Rx IP

Overview

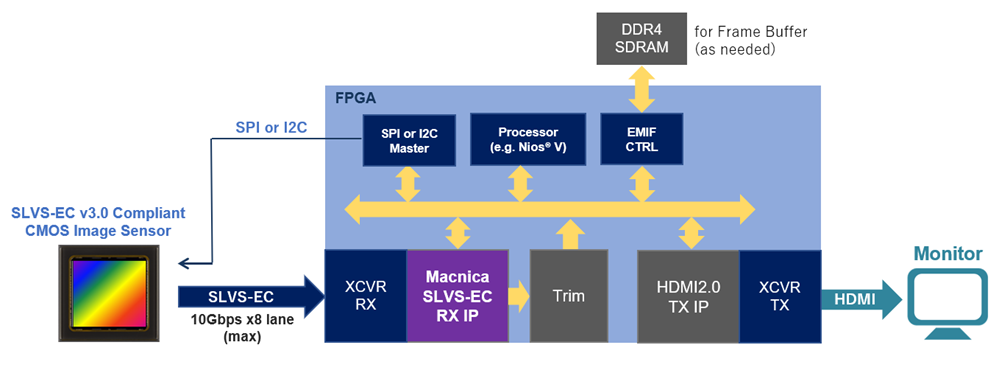

SLVS-EC Rx IP is an interface IP core conceived to run on multiple FPGAs. Using this IP, you can quickly and easily implement products that support the latest SLVS-EC standard v3.0. Our team has also created an evaluation platform to improve your time to market, by providing you with the tools you need to start your development.

- The FPGAs can receive signals directly from the SLVS-EC Interface.

- Compatible with the latest SLVS-EC Specification Version 3.0.

- Supports powerful De-Skew function. Enables board design without considering Skew that occurs between lanes.

- "Evaluation kit”(see below) is available for speedy evaluation at the actual device level.

Example of system configuration using this IP

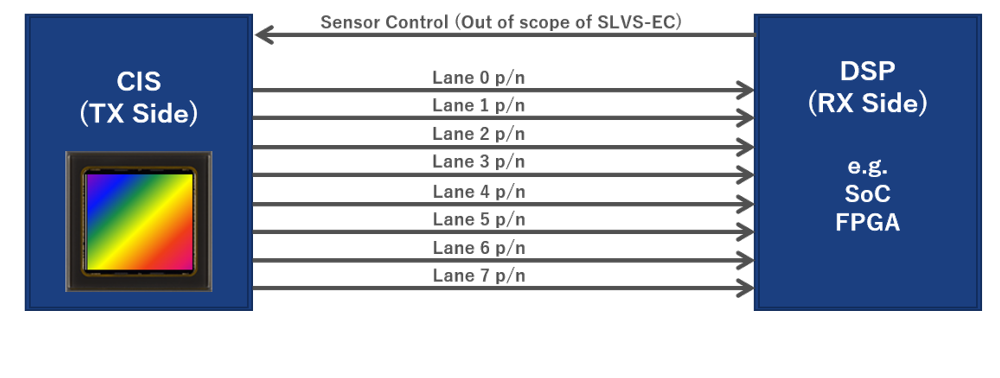

Overview of SLVS-EC Standard

- SLVS-EC (Scalable Low Voltage Signaling with Embedded Clock) is an interface standard for high-speed & high-resolution image sensors developed by Sony Semiconductor Solutions Corporation.

- The SLVS-EC standard is standardized by JIIA (Japan Industrial Imaging Association).

Features

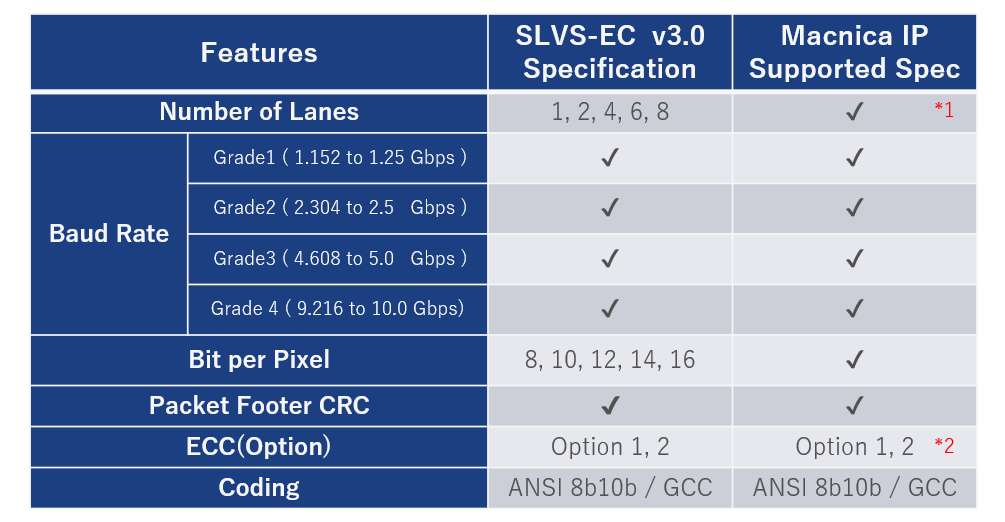

- SLVS-EC Specification Version 1.2/2.0 and the latest 3.0 are supported.

- Provides various functions defined in the SLVS-EC Link Layer.

- Selectable 32 or 64 pixel for output interface

- Supports 8, 10, 12, 14, 16 bit/pixel

- Realizes transfer with less overhead compared to conventional ANSI 8b10b by taking advantage of GCC (Gigabit Channel Coding) features added in the latest SLVS-EC Version 3.0.

- Supports error correction using Error Correction Code (ECC)

- Supports Byte to Pixel conversion in 1, 2, 4, 6, and 8 lane configurations.

- Header analysis and payload error detection.

- Compile options allow removal of unnecessary functions.

Specifications

Grade 4: New in SLVS-EC v3.0

*1: Fixed by compiler option

*2: Limited support for Option 2

Supported FPGA Families

Altera® FPGA

- Arria® 10 FPGA

- Agilex™ 7 FPGA

- Agilex™ 5 FPGA

AMD® FPGAs

- AMD Kintex™ UltraScale+™

For other FPGA families release schedule, please contact us.

More FPGA, ASICs & IPs Partners

CoaxPress IP

Macnica Vision makes it easy to develop cameras and other devices that will transfer image data from a camera to a PC with a frame grabber via a simple-to-install, 75Ω coaxial cable at up to 6.25 Gbps per lane. CoaXPress, defined by JIIA (the Japan Industrial Imaging Association) is one of the newest and fastest-growing interface standards for machine vision. The CoaXPress 1.1 & 2.0 Device Packages give you everything you need to develop products using the standard, from an encrypted RTL to a software library that will help you support GenICam, the software API for CoaXPress and other machine vision standards.

Features

- Compliant with CoaXPress Version 1.1.1 and Version 2.0

- Data transfer rate up to 6.25Gbps/lane (version 1.1.1) / 12.5Gbps/lane (version 2.0)

- Supports up to 4 Connections

- Supports up to 4 Streams

- Supports GenICam

- Certified and registered under the JIIA Interoperability Test

Supported Devices

- Cyclone 10 GX

- Arria 10 GX

*Please contact us about other devices.

Deliverables

- Encrypted RTL (Verilog HDL)

- Reference design

- Firmware for CoaXPress/GenICam including XML generator

- Documents